Xilinx Virtex-7 High-End Networking Card with Samtec FireFly

详情介绍

概览

电路功能与优势

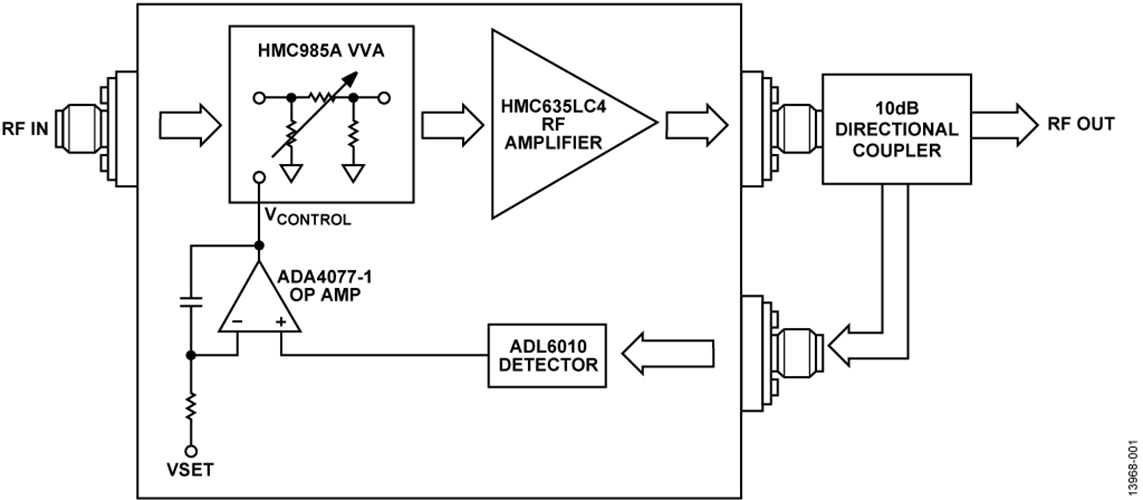

自动增益控制(AGC)电路在很多应用中都非常重要,例如频率合成器的幅度稳定、发射机输出功率控制或接收机动态范围优化。图1所示电路采用ADL6010检波器、HMC985A电压可变衰减器(VVA)和HMC635 RF放大器,在很宽的输入频率(20 GHz至37.5 GHz)和幅度范围内提供自动增益控制。在20 GHz和30 GHz之间,电路性能(通过本电路笔记中介绍的AGC品质因数来衡量)非常好。在30 GHz以上,电路的总增益会下降。然而,利用匹配技术(本电路笔记未予讨论)可以改善窄带性能。

该AGC电路适用于微波仪器仪表和雷达测量系统。

电路描述

许多RF应用要求对幅度进行非常精确的控制,使其随时间和温度的漂移最小化。举例来说,要求NBS可追溯校准的仪器就是有这种要求的应用例子,其校准间隔时间可能很长,比如每年一次或两次。其他应用包括相控阵雷达,其幅度和相位控制的精度限制了波束赋形精度。本电路采用的方法是将集成电路运算放大器用于环路控制器,通过出色的增益控制来补偿RF器件增益随输入幅度、RF频率和温度的变化。

实际操作中,VSET直流偏置控制输出幅度。根据环路的精度要求,最可能的应用是利用8位至12位DAC驱动此直流偏置。这种方法可以对RF输出幅度进行数字控制。虽然DAC不是本电路笔记的一部分,但有许多选项可用,例如ADI公司的 AD5621 12位nanoDAC。

AGC工作原理

此类AGC电路背后的核心思想是让RF信号的幅度保持稳定,RF信号可能随着频率、温度或时间而变化。通常,此电路有两路输入。第一路输入是给定幅度的RF输入,其包络需要稳定。第二路输入是施加于VSET引脚的的直流控制,正是利用此输入来设置输出幅度。图3显示了这种简单环路。

图3显示差动放大器用来比较VSET电压和检波器电路产生的电压。检波器将RF放大器输出幅度转换为直流电压。RF输入(X)在环路中间注入,故对RF输出(Y)而言,X任何变化的影响都被降至最低。只要总环路增益保持很高水平,这种效应便成立。通过以下等式可以阐释这种效应:

其中Gd为检波器增益。

从等式5可知,只要值Gd/10 >> 1,X的幅度对Y的幅度的影响便非常小。有两个因素可能影响X和Y之间的这种关系:检波器增益Gd和定向耦合器上的10 dB抽头。

但在CN-0390设计中,运放控制器电路周围构建了一个积分器,故环路直流增益仅受运算放大器的高开环直流增益限制。此增益足够高,使得AGC在控制环路范围内的平坦度接近理想水平。

像任何AGC电路一样,环路操作存在限制。对于给定范围的RF输入幅度和VSET控制电压,该环路闭合。这些限制也会随着频率改变而变化。一般而言,当VGAINCTRL (Z)节点介于−2.4 V和0 V之间(这是 HMC985AVVA的输入范围)时,该环路闭合,输出幅度保持平坦,不随RF输入变化而变化。

注意,检波器(VOUT与RF输入幅度的关系)和VVA(衰减与电压控制的关系)的传递函数具有明显的非线性特征(参见图5、图6和图7);其合并增益在RF输入和VSET输入的范围内有很大变化,并可能随频率和温度发生变化。利用控制环路中的积分器高增益来补偿这些效应。

实际构建的电路比图3所示的简单模型要更复杂。在实际电路中,VVA功能分属两个器件。第一个器件是 HMC985A VVA,其提供大约3 dB(VCTRL = −2.4 V时)到40 dB(VCTRL = 0 V时)的衰减。另一个器件是HMC635 RF放大器,其用于增益级,在目标频率范围内提供18 dB的增益。

AGC操作的直观方法

从概念上掌握AGC环路响应的另一种方法是理解当环路闭合时(−2.4 V > VGAINCTRL > −0 V),VSET控制电压等于 ADL6010 检波器的输出电压。在这一条件下,运放积分器处于平衡状态,积分器电容电荷稳定不变,不充电也不放电。当VSET处于静态时,如果RF输入幅度改变,则环路会作出响应,积分电容充电或放电,直至重新达到均衡。

当环路处于均衡状态时,ADL6010的输出等于VSET电压。这样,ADL6010传递函数就可以引用VSET电压(参见图5),以求得与此电压对应的ADL6010 RF输入功率。然后在此RF输入功率数值上增加10 dB(因为定向耦合器上有10 dB抽头),得到与给定VSET电压对应的输出功率。利用这种方法可以创建输出功率与VSET电压的关系表。VVA和ADL6010的传递函数是非线性的;因此,这种方法比建立这些传递函数的数学描述可能更为简单。

ADL6010包络检波器

该电路的最重要器件是ADL6010包络检波器。ADL6010的工作频率范围是500 MHz至45 GHz。如图4中的功能框图所示,ADL6010是一种基于二极管的检波器。如图5所示,ADL6010的响应曲线是非线性的,故而对此电路中的反馈环路进行直接分析是很困难的。

VVA和RF放大器组合

HMC985AHMC985A VVA的工作频率范围是10 GHz到40 GHz,提供的衰减范围是3 dB到近40 dB。HMC985A由两个pi-pad衰减器串联而成,第一个由VCTRL1控制,第二个由V CTRL2控制。通过连接V CTRL1和V CTRL2并将其一起驱动,可以实现大约3 dB到40 dB的综合衰减。电路中还串联了HMC635 RF放大器,完整的电压控制增益范围是15 dB增益到22 dB衰减。

HMC635 是一款GaAs放大器,需要一个负栅极电压(VGG),其必须与5 V VDD电源同时施加或先于后者施加。如果违反此VGG要求,HMC635可能受损。VGG典型值为−0.6 V,但为优化放大器性能,不同器件可能稍有出入。关于通过调整VGG来设置最优漏电流的信息,请参阅HMC635或其他GaAs放大器的数据手册。

为便于用户使用,实际构建的评估板使用二极管和电阻来将VGG偏置到约−0.6 V,这样就不需要单独的VGG电源。建议先施加−5 V供电轨,以便满足VGG要求。用户可移除此二极管,将单独的VGG电源施加于TP6。沿正方向移动VGG会提高电路的总增益,但代价是失真可能增加。

集成运算放大器和VSET控制详情

电路增益平衡时,ADL6010检波器输出电压等于外部施加的VSET。图8显示了一种确定运算放大器电路正确增益符号的直观方法。标签1表示环路中存在扰动,引起RF输出幅度提高,最有可能是输入幅度提高。ADL6010输入的RF幅度(标签2)也提高,ADL6010输出电压(标签3)同样如此。积分器输出电压上升,直至VSET等于ADL6010输出电压。因此,HMC985A VVA输入电压(标签4)提高(在−2.4 V到0 V的尺度上),进而导致VVA衰减提高,抵消RF输入的正扰动,确认反馈控制的符号正确。

ADL6010的响应曲线可用来分析电路控制范围。由于运算放大器的积分器功能,当VSET等于ADL6010输出电压时,环路处于平衡状态。1 V的VSET电压大致相当于4 dBm RF功率输入ADL6010。定向耦合器上有10 dB抽头,故现在的1 V VSET表示RF放大器的功率输出为14 dBm。观察VVA衰减曲线,考虑到RF放大器有18 dB增益,并且知道当VVA电压介于−2.4 V和0 V之间时环路闭合,便可创建VSET与RF输出功率的理想值表格。表1显示了预期RF输出功率与VSET值的关系,同时给出了AGC环路闭合的预期RF输入功率范围。举个例子,VSET = 0.1 V时,对于超低信号电平,环路处于最大增益状态(VVA = 3 dB衰减)。当RF输入功率上升至−20 dBm时达到拐点,此时环路闭合,当RF输入功率提高时,RF输出功率保持不变。当RF输入功率上升至17 dBm时达到VVA衰减限值,此时环路再次打开,增益控制丢失。

| VSET (V) | ADL6010输入功率(dBm) | 加上定向耦合器的10 dB (dBm) | 减去21 dB的RF放大器增益和衰减器增益1 (dBm) | RF输入,VATTEN = 0 V(40 dB衰减)(dBm) | RF放大器输入饱和所需的VVA衰减(dB) |

| 0.1 | -15 | -5 | -20 | 17 | 超出范围 |

| 0.2 | -10 | 0 | -15 | 超出额定最大输入功率 | 超出范围 |

| 0.3 | -7 | 3 | -12 | 超出额定最大输入功率 | 36 |

| 0.4 | -5 | 5 | -10 | 超出额定最大输入功率 | 34 |

| 0.5 | -2.5 | 7.5 | -7.5 | 超出额定最大输入功率 | 31.5 |

| 0.6 | 0 | 10 | -5 | 超出额定最大输入功率 | 29 |

| 0.7 | 1 | 11 | -4 | 超出额定最大输入功率 | 28 |

| 0.8 | 2 | 12 | -3 | 超出额定最大输入功率 | 27 |

| 0.9 | 3 | 13 | -2 | 超出额定最大输入功率 | 26 |

| 1.0 | 4 | 14 | -1 | 超出额定最大输入功率 | 25 |

| 1 假设最大增益、最小衰减(3 dB)。 | |||||

在该尺度的另一端,VSET = 1.0 V时,拐点直至RF输入功率达到4 dBm才出现,并且当RF输入功率达到电路的额定最大输入功率时,环路仍保持闭合。注意,HMC635数据手册规定P1 dB为21 dBm;HMC985A数据手册提供了输入功率最高达到24 dBm的特性曲线,用于此测试的发生器最大输出功率为20 dBm。图9显示了VSET与预期输入和输出功率的理想关系曲线,以及它与实测数据的对比。虽然理想曲线与实测数据确实略有偏差,但若假定衰减器和放大器的增益比数据手册给出的值小1 dB到2 dB(可能原因是此PCB上的RF匹配不够理想),则理想曲线将与实测数据非常接近。另外,图5所示的ADL6010传递函数是针对超低频率的。在较高频率时,ADL6010会轻微压缩,这解释了我们在VSET尺度较高部分看到的理想值与实测数据的差异。

图10和图11分别显示AFC电路在30 GHz和37.5 GHz下的响应曲线。注意,初始增益在30 GHz时下降,下降幅度不大于37.5 GHz时的降幅,并且在较高VSET电压下响应有压缩,限制了这些频率下VSET与RF输出功率的控制范围。在30 GHz时,VSET = 0.6 V至VSET =1.0 V的曲线互相重叠;在40 GHz时,VSET = 0.9 V至VSET =1.0 V的曲线互相重叠。

AGC品质因数

有多种方法可判断AGC环路的质量。

输出幅度平坦度与输入幅度变化的关系

输出幅度平坦度与输入幅度变化的关系是最直观明显的,同时也是此种电路之所以存在的原因。在低RF频率时,衰减器、RF放大器和检波器的组合增益足够高,可实现近乎理想的平坦度,如图9和图10所示。在37.5 GHz时,电路增益开始下降,平坦度性能随之降低,如图11所示。

正增益

理想情况下,即便输入信号非常小,AGC电路也能在很宽的输出幅度范围内保持增益平坦度。而实际上,性能是分区域的,有时总增益为正,有时总增益为负。在20 GHz时,如图9所示,在一个很大区域内,总增益为正。当频率提高到30 GHz时,然后再提高到37.5 GHz时,此正区域会缩小。

VSET范围和线性度

由于ADL6010响应的非线性,VSET与RF输出幅度的关系曲线也是非线性的。在20 GHz时,这种非线性表现为较高VSET电压下的曲线比较低VSET电压下的曲线靠得更近。在30 GHz时,VSET与输出幅度的关系被压缩得足够厉害,导致整体AGC响应在VSET = 0.6 V以上根本不变。37.5 GHz时的VSET响应打开得略多,但在VSET = 0.9 V以上仍被压缩。图12显示了一种略有不同的研究此关系的方法,其中绘制了20 GHz、30 GHz和37.5 GHz时RF输出幅度与VSET的关系曲线。

环路对输入幅度瞬变的响应

任何反馈环路都关心稳定性,AGC也不例外。为了估计此AGC环路的稳定性,在VSET端应用一个步进,然后测量运放积分器输出端的响应。如图13所示,响应为轻微欠阻尼状况,但显示出良好的稳定性。此瞬变是在RF频率为20 GHz时进行的。

相位噪声

对于模拟控制VGA,相位噪声可能是一个问题,常常需要权衡控制电压输入带宽与相位噪声性能下降程度。测量相位噪声性能下降程度的第一步必定是测量发生器本身,图14显示了输入频率为20 GHz且幅度为−10 dBm的情况。该图选择了相对较低的RF电平,使得环路处于高增益状态,任何相位噪声性能下降的影响都会最大化。图15显示了控制电压为0.1 V时AGC RF输出端的相位噪声,图16显示了控制电压为1.0 V时AGC RF输出端的相位噪声。如结果所示,在这些条件下相位噪声的提高并不突出。

常见变化

此电路可以从多方面加以改变。

选择HMC985A VVA和HMC635 RF放大器是因为其宽带宽能力,此电路可在20 GHz到37.5 GHz范围内进行评估。在−2.4 V到0 V的控制电压下,这些器件共同提供−22 dB到+15 dB的增益范围。其他VVA和RF放大器组合可在不同的频带上工作,提供不同的增益范围。由于环路控制运算放大器的电源范围,唯一限制是VVA控制电压必须在积分器所用运算放大器的输出电压范围内。

选择ADA4077-1的原因是其噪声低(6.9 nV/√Hz),并且支持采用±5 V电源供电。此应用对运算放大器的唯一绝对要求是其必须为电压反馈架构,支持采用±5 V电源供电,并且输出范围能够驱动所需的VVA范围。

增益缩放响应可以利用定向耦合器10 dB抽头或其他抽头上的衰减器来调整。这种情况下,输出功率与折合到ADL6010传递曲线的VSET以及衰减器和定向耦合器抽头的值有关。

可以用功率分路器代替定向耦合器。采用功率分路器的影响是会提高ADL6010输入幅度,从而使图9、图10和图11所示的响应曲线偏移。此偏移的代价是6 dB的输出功率。

本电路板和电路的设计覆盖频带是20 GHz至37.5 GHz。利用匹配技术可以改善窄带性能。请参考图20以了解窄带匹配如何提供最大的改善。

电路评估与测试

对于本测试所用的全部RF电缆,都必须在最高40 GHz下预先测量其损耗。AGC PCB上使用的SMA连接器为2.4 mm,因此必须提供与这些连接器相配的电缆和适配器。

设备要求

需要以下设备:

- EVAL-CN0390-EB1Z 电路评估板。

- +5 V电源,500 mA能力(用于 ADA4077-1运算放大器、HMC635 RF放大器和 ADL6010 检波器)。

- −5 V电源,100 mA能力(用于ADA4077-1运算放大器)。

- −0.6 V电源,用于HMC635上的VGG偏置,需要10 mA范围。此电源可选;可利用二极管和电阻来提供此偏置。PCB上有放置二极管和电阻的焊盘。务必先施加此VGG偏置,再在HMC635上施加+5 V偏置。务必不要同时施加+5 V VDD和VGG偏置。

- 0 V至3.0 V可调电源,用于VSET控制。只需mA范围的电流。

- CN-0390评估软件(从ftp://ftp.analog.com/pub/cftl/cn0390/下载)。此软件可选,因为该电路完全可以手动运行。C#.exe文件和源代码可从ADI公司获得。代码采用Microsoft Visual Studio C# 2012版编写。代码利用GPIB库控制RF发生器、VSET控制和频谱分析仪。所用的GPIB库来自National Instruments,由其免费提供。软件中的GPIB(SCPI代码)专门用于本节所述的仪器;虽然类似仪器(例如不同的频谱分析仪)的SCPI代码常常相同,但如果使用其他仪器,此代码可能无效。

- 能产生40 GHz连续波(CW)的信号发生器(推荐Keysight或Rohde & Schwarz)

- 支持40 GHz以上频率的频谱分析仪(Keysight或Rohde & Schwarz,或类似仪器)

- 10 dB定向耦合器(推荐Keysight或KRYTAR)

- 能够测量HMC985A VVA输入端控制电压范围的万用表。万用表的范围必须是−5 V至+5 V,因为当控制环路未闭合时,它可能摆动到电源电压。

- 带SMA连接器的同轴RF电缆,在40 GHz时的损耗最好尽可能低。PCB上使用的SMA连接器为Southwest Research的2.4 mm连接器。为降低损耗,应当用SMA管式连接器代替线缆来将定向耦合器连接到评估板。

开始使用

评估电路的步骤如下:

- RF发生器预设到20 GHz频率和−20 dBm输出功率。禁用发生器。设置频谱分析仪的中心频率为20 GHz,1 GHz范围,基准电平为20 dBm,RBW = 30 kHz。

- 将万用表连接到HMC985A VVA控制输入。

- 将电源电压设置为正确的值。将VSET设置为0 V。禁用所有电源。

- 将AGC的RF输出端连接到定向耦合器的输入端口。如可能,此连接应使用SMA管式连接器直连,因为再短的电缆也可能降低整体性能。定向耦合器的10 dB抽头必须通过尽可能短的电缆连接到AGC PCB的检波器输入。

- 按照图18所示连接所有其他电缆和电源。

- 先接通−5 V电源以偏置HMC635上的VGG,再接通+5 V电源。方便的话,两个电源可以同时接通;但+5 V电源不得先于−5 V电源接通。

- 检查+5 V、−5 V和−0.6 V电源的电流。其读数必须与以下值相似:

- +5 V电源,300 mA

- −5 V电源, 10 mA

- −0.6 V电源(如使用外部电源),1 mA

- 接通VSET电源。评估过程中会改变VSET。电流不得超过5 mA。

- 使能RF发生器。

在手动模式下运行电路

电路现在能够执行全部功能。RF发生器的输入幅度必须初始设置为−20 dBm。请勿超过+20 dBm,因为+20 dBm已接近HMC635 RF放大器的输入压缩限值。RF发生器功率设置为−20 dBm时,VVA控制电压可以达到−5 V供电轨。采用幅度非常低的信号时,环路使增益达到最大,故积分器输出电压始终低于−2.4 V,直至RF幅度高到足以使环路闭合为止。当RF功率提高时,用户最先看到的是频谱分析仪指示的输出功率以dB/dB的比例提高。然而,随着RF输入功率提高并达到AGC响应曲线的拐点,环路就会闭合,VVA控制电压移动到−2.4 V。此时,环路在最小信号输入下闭合,因此仍会尝试将自身设置到最大增益。随着功率进一步提高,频谱分析仪上的幅度无明显变化,因为环路会补偿输入电平的变化。相反,当功率提高时,用户看到VVA控制电压从−2.4 V提高到0 V。给定VVA、RF放大器和检波器的增益,当输入功率≤ +20 dBm时,VVA控制电压不会一路变到0 V,因此AGC斜率保持平坦。

如果所有结果都与前面所说的相同,那么现在就可以在不同的RF幅度、频率和VSET值下评估该电路。

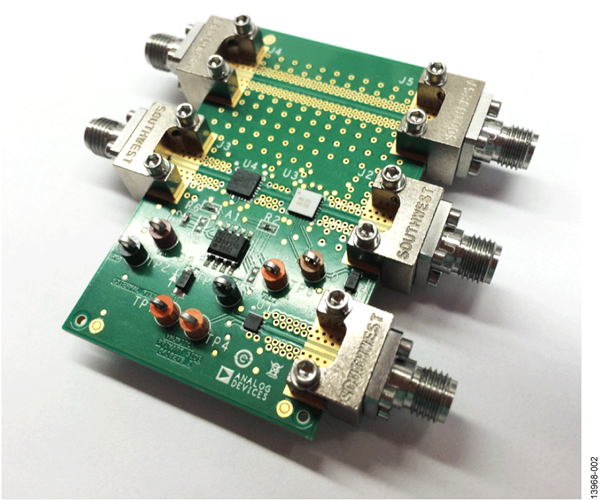

PCB设计

针对20 GHz到40 GHz的宽带工作范围的PCB设计不是一件轻而易举的事。PCB采用了接地共面波导技术,并在PCB上增加了一条测试走线以验证50 Ω走线结构。带电源和信号连接的整体布局如图17所示。实际测试设置中的PCB如图18所示。注意外部10 dB定向耦合器的连接,RF输入直接连到RF发生器,从而无需补偿电缆损耗。

完整的设计支持包,包括布局、原理图和物料清单,可从 www.analog.com/CN0390-DesignSupport下载。

验证RF走线质量和电路S参数

PCB在Cadence Allegro中设计。所有CAD设计文件均随本电路笔记一同提供。为实现高达40 GHz的50 Ω走线质量,我们提取了Allegro设计文件,然后在ADS中仿真。

S参数S11、S22、S21和S12如图19所示。正如数据所示,即使进行事先设计和仿真,23 GHz至28 GHz区域中的回波损耗也比最优值小。30 GHz至40 GHz范围中的性能要好得多。

图20显示了PCB上有源电路的双端口S参数(RF输入、RF输出)。从20 GHz到40 GHz,增益性能(S21)有滚降。增益性能中还有零点,这与测试走线中显示的回波损耗问题是一致的。

- 加入我的myAnalog 登录 myAnalog