光电二极管放大器

详情介绍

概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- AD9552/PCBZ ($149.50) AD9552 evaluation board used to evaluate this circuit. Please see "Circuit Evaluation & Test" section for more information.

- ADCLK854/PCBZ ($190.00) ADCLK854 evaluation board used to evaluate this circuit. Please see "Circuit Evaluation & Test" section for connection information.

优势和特点

- 灵活的时钟分配

- 引脚可编程

- 无需软件

- 时钟频率最高达900 MHz

电路功能与优势

振荡器上变频器AD9552 和LVDS/CMOS时钟扇出缓冲器ADCLK854共同构成灵活的引脚可编程时钟分配解决方案。AD9552配有一个SPI端口,用于对器件进行编程。此接口支持最高达900 MHz的宽输出频率范围。另一方面,它也可以通过引脚编程,从而简化许多不需要软件可编程性能的设计应用。

在引脚可编程模式下,最多可提供64种标准输出频率,具体视输入频率选择而定。因此,AD9552可以像频率引脚可编程VCXO一样工作。此外,AD9552还能采用输入端的晶体谐振器工作,以提供更大的灵活性。AD9552的简化框图如图1所示。

图1. 振荡器上变频器AD9552简化框图

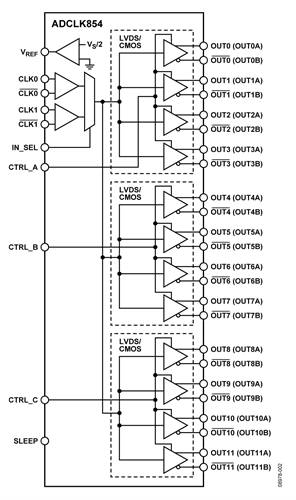

ADCLK854是一款时钟扇出缓冲器,其LVDS和1.8 V CMOS输出均可通过引脚进行编程。ADCLK854提供最多12路LVDS输出、24路CMOS输出或二者的组合。如果需要较少的输出和/或不同的输出逻辑选择,可以用ADI公司其它几个时钟扇出缓冲器代替ADCLK854。ADCLK854简化框图如图2所示。

图2. 时钟扇出缓冲器ADCLK854简化框图

电路描述

图3的简化电路显示AD9552与ADCLK854客户评估板之间的设置。AD9552可采用26 MHz晶体谐振器工作。然后,AD9552 LVPECL输出驱动ADCLK854评估板,以实现LVDS和/或CMOS扇出功能。选择LVPECL输出是因为它具有较低的抖动和相位噪声。

对于低抖动时钟分配,AD9552和ADCLK854是非常合适的组合。两款器件均具有引脚可编程特性,因而可实现独立的时钟发生器解决方案,无需将接口控制线连回FPGA或微控制器。此外,两款器件的尺寸均很小。图3给出了简化电路框图。有关内部连接和材料清单的详细信息,请参考 AD9552 评估板 和 ADCLK854 评估板文档。

图3. AD9552和ADCLK854电路组合示意图

下面的程序说明如何使用板上跳线和拨动开关对AD9552评估板进行手动编程,以便设置用于所选输入和输出频率的逻辑电平。本例中,晶振频率为26 MHz,输出频率为625 MHz。

- 确保跳线JMP3处于手动控制位置。

- 确认连接器P2上的所有五个跳线均已移除。

- 将S3拨动开关的位置设为0111,表示在使用26 MHz晶振。

- 将S2拨动开关的位置设为0010,并将S1拨动开关的位置设为0011。

- 将示波器、频谱分析仪或其它实验室设备与板右上侧J3至J6 SMA连接器中的任一个相连。

- 将评估板插入USB端口,以提供电源。

- OUT1 SMA连接器上应能观察到625 MHz的频率。

- 如果需要其它输出频率,请从USB端口断开。然后改变拨动开关设置,再次连接USB端口。

每次设置拨动开关之后,必须移除USB电缆,使AD9552断电,以便对AD9552重新编程。有关引脚编程的详细说明,请参考AD9552数据手册。

ADCLK854输出也是引脚可编程的,可提供最多12路差分LVDS输出或24路单端1.8 V CMOS输出。跳线CTRL_A、CTRL_B、CTRL_C和SLEEP用于配置输出。欲将输出配置为所需设置,请参考表1。

表1. ADCLK845 Configuration

| CTRL_A | Logic 0 = LVDS; Logic 1 = CMOS |

Output 0 to Output 3 |

| CTRL_B | Logic 0 = LVDS; Logic 1 = CMOS |

Output 4 to Output 7 |

| CTRL_C | Logic 0 = LVDS; Logic 1 = CMOS |

Output 8 to Output 11 |

| SLEEP | Logic 0 = LVDS; Logic 1 = CMOS |

Output 0 to Output 11 |

以下图4和图5中的绝对相位噪声和频谱图来自时钟扇出缓冲器ADCLK854的LVDS输出。

图4. 625 MHz时的ADCLK854 LVDS输出相位噪声(杂散关闭)

图5. 使用ADCLK854评估板的ADCLK854输出频谱(LVDS输出)